# **ECE 469** — Power Electronics Laboratory

## LABORATORY INFORMATION AND GUIDE

with

Chapter 18 of *ELEMENTS OF POWER ELECTRONICS*

Prof. P. T. Krein

Department of Electrical and Computer Engineering

University of Illinois

Urbana, Illinois

Version 2.5 — August 2012

Copyright @ 1988-2012 Philip T. Krein. All rights reserved.

# Contents

| Introductory Material                                             | iii      |

|-------------------------------------------------------------------|----------|

| Preface and Acknowledgements                                      | iii      |

| Expected Schedule                                                 | iii      |

| Introduction                                                      | iv       |

| Safety                                                            | v        |

| Equipment and Lab Orientation                                     | vii      |

| Introduction                                                      | vii      |

| Map of the Facility and Electrical Panels                         | vii      |

| The Lab Workbenches                                               | x        |

| Course Organization and Requirements                              | xiii     |

| The Lab Notebook                                                  | xiv      |

| The Lab Report                                                    | xvi      |

| The Title Page                                                    | xvi      |

| Abstract                                                          | xvi      |

| Conclusion                                                        | xviii    |

| References                                                        | xviii    |

| Appendix                                                          | xviii    |

| DEMONSTRATION #1 — Introduction to the Laboratory                 | 1        |

| EXPERIMENT #1 — Basic Rectifier Circuits                          | 11       |

| EXPERIMENT #2 — Ac-Dc Conversion, Part I: Single-Phase Conversion | on21     |

| EXPERIMENT #3 — Ac-Dc Conversion, Part II: Polyphase Conversion   | 29       |

| EXPERIMENT #4 — Dc-Dc Conversion, Part I: One-Quadrant Convert    | ters35   |

| EXPERIMENT #5 — Dc-Dc Conversion, Part II: Converters for Motor   | Drives43 |

| EXPERIMENT #6 — Dc-Ac Conversion, Part I: Voltage-Sourced Inverters             | 53       |

|---------------------------------------------------------------------------------|----------|

| EXPERIMENT #7 — Dc-Ac Conversion, Part II: Pulse Width Modulation Inverters     | 61       |

| EXPERIMENT #8 — Passive Components, Part I: Models for Real Capacitors and Indu | uctors67 |

| EXPERIMENT #9 — Passive Components, Part II: Magnetics                          | 77       |

| Design Project — Part I                                                         | 83       |

| Design Project — Part II                                                        | 91       |

| Summary Specification Sheets for Parts                                          | 100      |

| Design Project — Part III                                                       | 105      |

| APPENDICIES                                                                     | 112      |

| Standard Resistor Values                                                        | 112      |

| Common Waveforms                                                                | 114      |

| Index                                                                           | 115      |

| CHAPTER 18 — The Special Needs of Converter Experiments                         | 18-2     |

## **Introductory Material**

#### **Preface and Acknowledgements**

Power electronics studies the application of semiconductor devices to the conversion and control of electrical energy. The field is driving an era of rapid change in all aspects of electrical energy. The Power Electronics Laboratory course — one of very few offered at the undergraduate level in the United States — seeks to enhance general material with practice and hands-on experience. The laboratory course provides instruction in general lab practices, measurement methods, and with the design and operation of several common circuits relevant to the field of power electronics. It also provides experience with common components such as motors, batteries, magnetic devices, and power semiconductors. The course has a significant design component. The final weeks of the term are devoted to a power converter design project.

The equipment and instrumentation for ECE 469 were updated substantially in 2006, with additional updates in 2008. A bench reconfiguration project has been carried out in 2011. The building electrical system was completely rebuilt in 2010. Many people have helped in a wide variety of ways in the past, and their efforts are appreciated. The 2006 project owes a great deal to Z. Sorchini and J. Kimball, and special thanks go to them. Updates by R. Balog have been of great value. The generous support of The Grainger Foundation has been instrumental in developing and improving the laboratory. The efforts of the ECE Electronics Shop and the ECE Machine Shop in preparing the benches and equipment is gratefully acknowledged.

Student feedback is encouraged throughout the semester. Your input will help make the course more interesting and enjoyable, and will increase its value over time. Comments are always appreciated. Experiments and other work can and will be modified quickly if the need arises. The course is designed as an advanced laboratory, primarily for seniors and graduate students. You will find that procedural details are up to the student teams. The requirements for lab reports and procedures reflect the standards of a productive industrial research and development lab more than the relatively routine work in beginning courses.

#### **Expected Schedule**

The schedule will be provided during the first week of classes.

#### Introduction

Power electronics is a broad area. Experts in the field find a need for knowledge in advanced circuit theory, electric power equipment, electromagnetic design, radiation, semiconductor physics and processing, analog and digital circuit design, control systems, and a tremendous range of sub-areas. Major applications addressed by power electronics include:

- ·Energy conversion for solar, wind, fuel cell, and other alternative resources.

- ·Advanced high-power low-voltage power supplies for computers and integrated electronics.

- ·Efficient low-power supplies for networks and portable products.

- ·Hardware to implement intelligent electricity grids, at all levels.

- ·Power conversion needs and power controllers for aircraft, spacecraft, and marine use.

- ·Electronic controllers for motor drives and other industrial equipment.

- •Drives and chargers for electric and hybrid vehicles.

- ·Uninterruptible power supplies for backup power or critical needs.

- ·High-voltage direct current transmission equipment and other power processing in utility systems.

- ·Small, highly efficient, switching power supplies for general use.

Such a broad range of topics requires many years of training and experience in electrical engineering. The objectives of the Power Electronics Laboratory course are to provide working experience with the power electronics concepts presented in the power electronics lecture course, while giving students knowledge of the special measurement and design techniques of this subject. The goal is to give students a "running start," that can lead to a useful understanding of the field in one semester. The material allows students to design complete switching power supplies by the end of the semester, and prepares students to interact with power supply builders, designers, and customers in industry. Most of you will be surprised at how pervasive power electronics has become — and at how few people have a deep understanding of the field.

Power electronics can be defined as the area that deals with application of electronic devices for control and conversion of electric power. In particular, a power electronic circuit is intended to control or convert power at levels far above the device ratings. With this in mind, the situations encountered in the power electronics laboratory course will often be unusual in an electronics setting. Safety rules are important, both for the people involved and for the equipment. Semiconductor devices react very quickly to conditions — and thus make excellent, expensive, "fuses." Please study and observe the safety rules below.

#### Safety

The Power Electronics Laboratory deals with power levels much higher than those in most electronics settings. In ECE 469, the voltages will usually be kept low to minimize hazards. Be careful when working with spinning motors, and parts that can become hot. Most of our equipment is rugged, but some delicate instruments are required for our experiments. Even rugged instruments can be damaged when mishandled or driven beyond ratings. Please follow the safety precautions to avoid injury, discomfort, lost lab time, and expensive repairs.

- •GROUND! Be aware of which connections are grounded, and which are not. The most common cause of equipment damage is unintended shorts to ground. Remember that oscilloscopes are designed to measure voltage relative to ground, not between two arbitrary points.

- •RATINGS! Before applying power, check that the voltage, current, and power levels you expect to see do not violate any ratings. What is the power you expect in a given resistor?

- •**HEAT! Small parts can become hot** enough to cause burns with as little as one watt applied to them. Even large resistors will become hot if five watts or so are applied.

- •CAREFUL WORKMANSHIP! Check and recheck all connections before applying power. Plan ahead: consider the effects of a circuit change before trying it. Use the right wires and connectors for the job, and keep your bench neat.

- •WHEN IN DOUBT, SHUT IT OFF! Do not manipulate circuits or make changes with power applied.

- •LIVE PARTS! Most semiconductor devices have an electrical connection to the case. Assume that anything touching the case is part of the circuit and is connected. Avoid tools and other metallic objects around live circuits. Keep beverage containers away from your bench.

- •Neckties and loose clothing should not be worn when working with motors. Be sure motors are not free to move about or come in contact with circuitry.

- •Remember the effects of inductive circuits high voltages can occur if you attempt to disconnect an inductor when current is flowing.

#### •EMERGENCY PHONE NUMBER:9-911

The laboratory is equipped with an emergency electrical shutoff system. When *any* red button (located throughout the room) is pushed, power is disconnected from *all* room panels. *Room lights and the wall duplex outlets used for instrument power and low-power experiments are not affected.* If the emergency system operates, and you are without power, inform your instructor. It is your instructor's task to restore power when it is safe to do so. Each workbench is connected to power through a set of line cords. The large line cords are connected to two front panel switches labelled "3φ mains" and "dc mains." The standard ac line cord is connected to the switch on the bench

Power Electronics Laboratory Manual -- Introductory Material

outlet column. Your bench can be de-energized by shutting off these three switches.

#### **Equipment and Lab Orientation**

#### Introduction

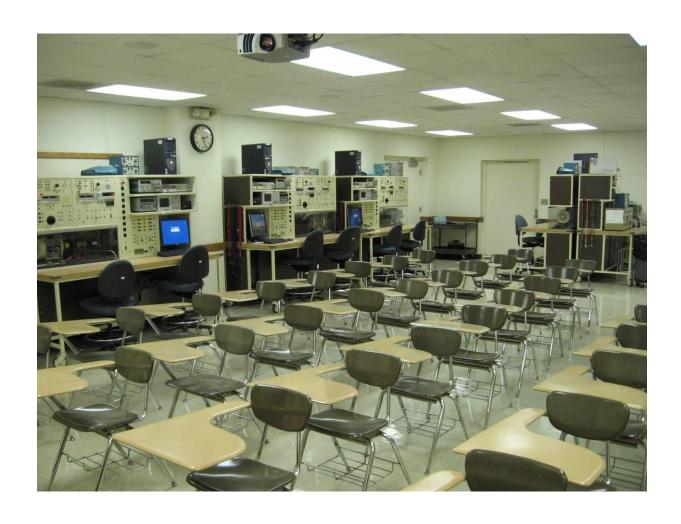

The Grainger Electrical Machinery Laboratory was funded through a grant from the Grainger Foundation. Over the past five years, the equipment and support has been completely renovated, most recently including an entirely new power system in Everitt Laboratory. The facility rivals many modern industrial research counterparts in terms of safety and instrumentation.

The laboratory has a central panel for its primary power sources, a set of workstation panels to distribute power throughout the room, and special lab benches that are the primary tool for all work. The benches hold rotating machines, dedicated power meters, an instrument rack, a cable rack, and connection panels. Extra instrumentation and equipment are stored in cabinets at the bottom of each bench.

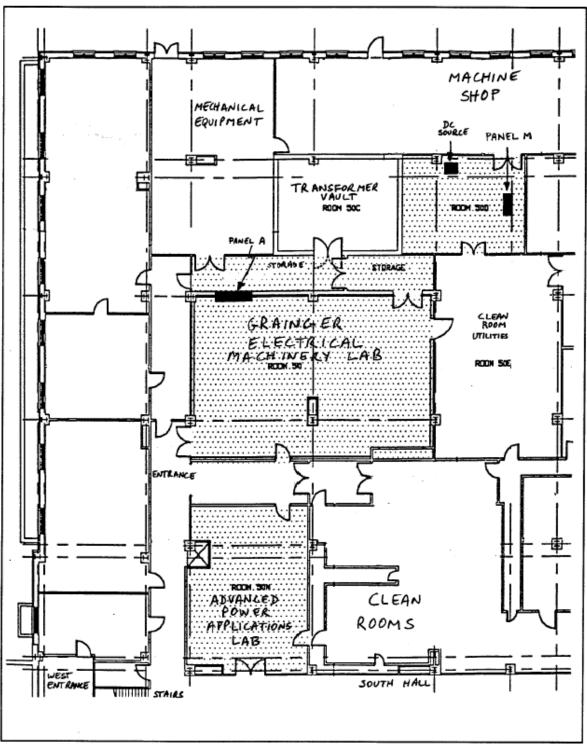

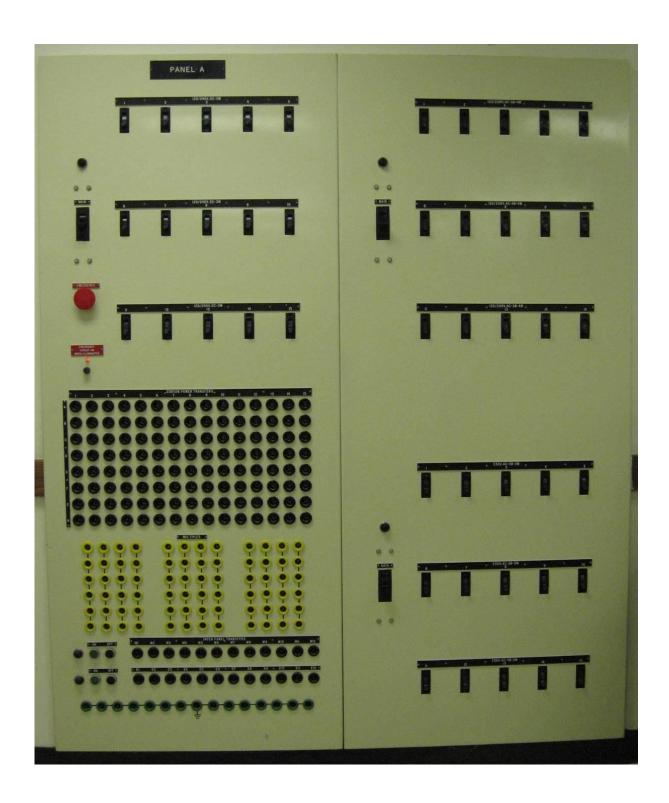

## Map of the Facility and Electrical Panels

The laboratory is located in room 50 (no suffix) in Everitt Laboratory. A map of the lab and adjacent facilities appears in Figure 1. A storage area is located just north of the laboratory. Motors and extra instruments are kept in that area. Across the hall to the south is the Advanced Power Applications Laboratory, a research facility which shares many of the same features. The main laboratory is supplied by two dedicated transformers which convert building power to independent 60 Hz ac power supplies at 208 V three-phase and 230 V three phase, each at up to 150 kVA (or more than 400 A at 208 V three-phase). A separate dc power supply system delivers  $\pm$  120 V at up to 24 kW. Power from the regular building supply is used for instruments and low-power experiments. These ac and dc supplies are distributed to the laboratory through a main "Panel M" located in room 50D, and delivered to the room master "Panel A." Panel A provides power through circuit breakers to the workstation panels, and also includes an interconnect set for experiments that involve multiple benches. Both panels M and A are intended to be operated by your instructor only. There are jacks on Panel A which connect to Panel M. Panel M, in turn, provides access to master panels elsewhere in Everitt Lab. From the master panels, wiring can be routed to most laboratories and many classrooms throughout the building. Up to 30 A can be imposed on any of these wires.

The master circuit breakers in Panel A have what is called a "shunt trip" mechanism. They can be turned off with a short pulse of ac power. When any of the large red "panic buttons" throughout the room is pushed, all master breakers in Panel A are forced to shut off. When this occurs, power is cut off at all lab station panels throughout the room. This provides an emergency disconnect capability. It does not affect lights or regular wall outlets in the lab.

Figure 1. The Grainger Electrical Machinery Laboratory and surroundings.

Figure 2. Front view of workstation panel.

A view of one of the fourteen workstation panels is provided in Figure 2. The top portion contains three power outlets for convenient access to various high-power supplies. One of these is a 120/208 V three-phase source, which is also connected to an adjacent set of duplex outlets. The center of the panel holds eight "transfer jacks," wired to the interconnect area of Panel A. There is a ground jack for access to a solid earth ground. The bottom of the panel allows access to low-level computer and communication lines. Line cords on each lab workbench make connections to the various power sources convenient. Each of the three large lab station outlets has a corresponding circuit breaker in Panel A. Twisted-pair internet access at 100 Mbaud is adjacent to most panels.

#### The Lab Workbenches

#### **Overview**

Each power lab bench is designed as a complete test station, with its own safety features and protective mechanisms. The benches have space for instrument operation and for storage, rotating machines, and power connections. A photograph is shown in Figure 3, with a layout in Figure 4. There are two functionally identical bench versions — a right-hand unit and a left-hand unit.

Figure 3. Laboratory bench, "left-hand" version.

The benches plug into the workstation panel outlets with power line cords accessed through the bench "window" behind the computer monitor. Many panel jacks on your bench have been pre-wired internally for your convenience. These jacks have identical labels. They allow short, organized connections. *Please be aware of these labels, and respect them.* The benches are divided into four major sections: input power handling and distribution, rotating machine connection panels, the instrument rack, and the load patch area.

The power line cords have incompatible plugs to prevent errors in power access. They are of the twist-lock style to prevent accidental removal. Three-phase ac power to the bench can be taken from either the  $120/208 \, \text{V}$  source or the 230 V source. However, these sources are not used simultaneously. A double-throw center-off switch located beneath the bench must be set to select the proper source. In any case, three-phase ac power is wired to the " $3\phi$  mains" switch on the bench front panel. When this switch is off, no three-phase power will appear at the bench panels. Dc power to the bench is routed from the line cord, through a fuse box, and then to the "dc mains" switch on the front panel. As with ac power, turning this switch off will remove all panel access to the dc source.

Figure 4. The laboratory workbench.

The single-phase ac instrument power is routed from the familiar  $1\phi$  line cord to the outlet column near the center of the bench, to outlets in the instrument rack, and to internal instrument power through a front-panel circuit breaker. The single-phase line cord should be plugged into the wall duplex outlet near the floor so that computers and instruments will not be affected by use of the room panic buttons. The other cords should be plugged in only as necessary for power access. Each bench can be shut off by turning off the  $3\phi$  mains switch, the dc mains switch, and the instrument power switch.

## <u>Inventory</u>

Each bench is permanently equipped with the following:

- Variable three-phase ac transformer, 0-230 V, 0-10 A.

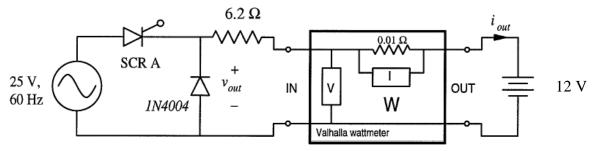

- Valhalla Scientific model 2101 RMS volt-ampere-wattmeter and Valhalla Scientific model 2111 RMS voltampere-power factor-wattmeter.

- •Fluke dual-display multimeter.

- Westinghouse Power Miser TRIAC-based ac motor starter.

- •Kollmorgan PWM ac servodrive and permanent-magnet motor with encoder.

- •One, two, or three-phase transformer set, 120 V/25.2 V, 0-3 A.

- •Two 300  $\Omega$  power potentiometers, 100 W.

- •Power resistor,  $100 \Omega$ , 150 W.

- •Three 3-pole switches, 30 A.

- •Two 1-pole switches, 6 A.

- •Machine set.

In addition, each bench is supplied with the following equipment:

- •Tektronix model TDS3034 digital oscilloscope with TCP/IP interface.

- •Tektronix model TCP202 current probe and P5205 differential voltage probe.

- •Tektronix model TM504 instrument plug-in unit with multimeters, function generator, and power supply.

- •Kenwood PD56-10AD power supply, 0-56 V, 0-10 A.

- •Hewlett-Packard model 6060B electronic load, 3-60 V, 0-60 A, 300 W.

- •Pentium computer, running Windows XP or Windows 7.

- Dual power supplies,  $\pm$  12 V and + 5 V.

- Temperature probe.

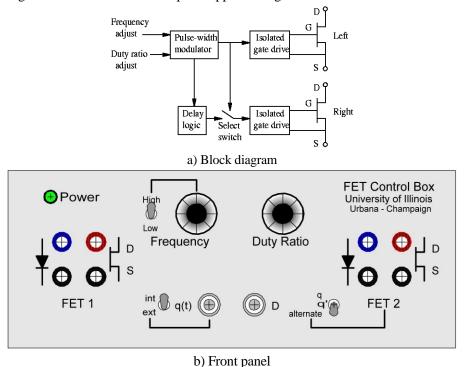

- Isolated dual power FET control box, 0-300 V or more, 0-15 A or more.

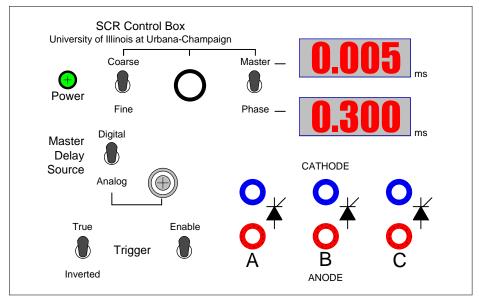

- Isolated one-two-three phase SCR control box, 0-300 V or more, 0-20 A or more.

- •PWM audio amplifier, single channel.

- •Three power resistor boxes, each with ten 500  $\Omega$  resistors.

- •Three capacitor boxes, each with eight 6 µF capacitors.

- •Three transformer boxes, 1 kVA each.

- •Lead rack with banana and BNC leads of various lengths.

Additional power supplies, meters, and small motors are stored in the cabinets. There is an extensive selection of power resistors, inductors, magnetic cores and parts, power semiconductors, heat sinks, tools, protoboards, and other general parts.

Special purpose instruments expected to be available for shared use include:

- •Hewlett-Packard model 4195A network/spectrum analyzer.

- •Tektronix model 371 power semiconductor curve tracer.

- •Laser printer.

- •Philips model PM6303 automatic RCL meter.

Please make an effort to keep track of the equipment at your bench, especially portable items such as probes. It is important that you do measurements carefully and in an organized fashion. Equipment damage is expensive and can cause time delays or inconvenience for you. Look over your station at the beginning of each lab.

### **Course Organization and Requirements**

The course consists of about fourteen lab sessions and a weekly lecture/discussion session. The hour of lecture/discussion each week will provide specific lab preparation, opportunity for general questions, time for elaboration on practical power electronics topics, and demonstrations. Required efforts are as follows:

- A short pre-lab assignment accompanies each experiment. The purpose of this assignment is to help

you prepare for the experiment. The problems apply directly to the procedure or report. Pre-labs must

be completed and turned in before performing the given experiment. Late pre-lab assignments will

not be accepted.

- The experiments and reports are semi-formal in nature. Proper lab notebooks must be maintained by all students. Reports are written independently by each individual, and follow the format given below. Correct spelling, grammar, and punctuation are expected. Most reports will cover a group of experiments.

- The final class session involves a brief oral presentation. Here, the design project is described and demonstrated.

Care and neatness in the maintenance of lab notebooks and in the preparation of reports is important. Your instructors will be pleased to assist you in generating quality work.

As you know, it is difficult to make up missed laboratory work. Please notify your instructor as soon as possible if illness or similar emergency prevents your attendance. In other cases, arrangements can sometimes be made, given enough advance warning; however, time demands on your instructors are such that **make-up** sessions will not be held without acceptable excuse.

Lab sessions will be divided into two major categories:

<u>Demonstrations</u> are conducted by your instructor, and usually involve complicated laboratory work. They

allow experiments which require extensive setup time, unusual equipment, or intricate measurements. In the case of demonstrations, the pre-lab assignments serve to highlight major points. In general, you will be expected to take notes and record data during demonstrations, for use in preparing reports.

<u>Experiments</u> are conducted by students in small teams. For each experiment, one team member serves as leader, another as recorder, and any others as helpers. Teams will be assigned early in the semester, and will generally stay the same throughout the course. Team duties rotate for each experiment.

#### The Lab Notebook

The laboratory notebook is a crucial tool for work in any experimental environment. A notebook used in a research lab, a development area, or even on the factory floor is probably the most valuable piece of gear in the engineer's arsenal. The purpose of the notebook is to provide a complete *permanent* record of your practical work. Why a notebook? It allows you to reproduce your own work, or to refer to it without having to duplicate the effort. It provides a single place that tracks your work in a consistent way. It provides a permanent physical record for legal purposes. Often, it permits us to "reverse engineer," and find errors of record or procedure.

The notebook is your record, but in most industry practice is the property of your employer. For this reason, many companies have specific rules about notebook format, content, and usage. In the ECE 469 lab, your notebook will eventually become your property (although for the moment you should act as if it belongs to the State of Illinois). It should include:

- Diagrams of all circuits used in the lab. If the circuit is identical or almost identical to one in your procedure or book, you may reference (not copy) it. The important factor is to be able to reproduce your setup in case of errors.

- Procedures and actions. (But do not repeat steps in the lab manual.) The idea is to provide enough information so that you could repeat the experiment.

- Equipment used. (List only your bench number if you used only the standard bench equipment.) The model and serial numbers of instruments and equipment should be recorded in your notebook. This is mainly for your protection in case a scale is misread or equipment is defective.

- All data generated in the experiment. Be sure to include units and scale settings. For example, oscilloscope data might read "data in display divisions, 50 mA/div," and then list the numbers read.

Use data in its most primitive form. Do not perform scaling or calculations when data is first recorded.

The objective is to minimize errors.

- If hard copy plots or prints are generated, write the date on them and tape them into the notebook at the appropriate location.

- Names of the experiment team, with a summary of duties. Each team member should maintain a notebook in each session, although the recorder performs the bulk of this task each week. The recorder should provide copies of the original pages to all team members before leaving each week. Even though the recorder keeps notes for a given week, other team members should summarize their efforts in their own notebooks.

- Dated initials of the recorder on each page used for a given day's work.

- Your instructor's signature and signatures of all team members on the last page of the day's work.

It is entirely permissible to include calculations, observations, and even speculations in your notebook, provided these are clearly marked and kept apart from experimental data and actual bench work.

The notebook must be a bound book with permanent, pre-printed page numbers. Within these requirements, any type is acceptable. Do not use loose sheets for data or other information. It is absolutely not acceptable to recopy information into the notebook at a later time. Notebook errors should be crossed out (not obliterated) and initialed and dated by the recorder. Be sure to initial and date each page of your notebook as it is filled. Remember that paper is cheap: start a new page rather than cramming extra information onto one sheet. *The notebook must be kept in ink!*

Keeping a complete lab notebook sometimes seems inconvenient, but in the long run saves a tremendous amount of time and effort. Some of the uses of an official notebook are:

- A record of your personal efforts for use with your manager or instructor.

- A history of work on a particular project or circuit. This avoids the need for duplicated effort.

- An official record for patent applications. If a patent is challenged in court, the notebook is the key

document to be used.

- A complete technical record for use in reports, articles, specification documents, and drawings.

- Identification of points at which errors were made.

The notebook is the "who, what, where, when, how" of the technical world. Billions of dollars are wasted each year duplicating efforts which were not carefully documented or defending patents based on sketchy lab data.

#### The Lab Report

An experiment is not considered complete until the results have been properly reported. One of the primary tasks of an engineer is to *interpret* results of work, rather than just to gather data. A good report helps you understand the concepts in the experiment, and also helps you when you wish to discuss and communicate those results with others. A high-quality report allows a reader to understand your results and gain the benefits of your insights. Working engineers often mention technical writing as an area in which they could have used better preparation — because of the need for good engineering reports. To give you some additional practice along these lines, lab reports for ECE 469 are semi-formal in style. They should be prepared with a word processor and laser-quality printer. The computers in room 50 can be used if necessary. Be sure to take advantage of spell-checking and similar features.

The report has six elements:

- 1. **The Title Page**. This must show the report title, author, dates, and names and duties of group members.

- 1a. **Table of Contents**. Required only on the Design Project report. This should show the locations of all headings and major subheadings.

- 2. **Abstract**. A one paragraph summary of the report, including:

- → A brief but clear summary of the objectives and results.

- →An indication of the system studied, loads used, and the basic work performed.

- 3.Discussion. This is the body of the report, and may contain subheadings as needed. It should report on the laboratory effort. It should summarize the data and any calculated results. The Discussion should briefly describe the important theory and concepts. It should compare measured results with those expected, and contrast the various cases studied. It should discuss important sources of error and their relevance to the results. Finally, it should discuss any difficulties encountered and suggest what might have been done differently. Study questions assigned in class or in lab procedures should be addressed in the Discussion. Figures, tables, and circuit diagrams are encouraged. Laboratory reports in which the discussion merely paraphrases the lab manual are not acceptable. Suggested subheadings include:

## $\rightarrow$ Theory

Brief overview of theory and the methods used for the experiment and its analysis. This should provide sufficient background for the reader to understand what you did and why. It should help the reader follow along with the rest of your discussion. *Detailed or basic theory should not be repeated from the lab manual or textbook.*

→ Results

This portion provides an organized summary of your data and calculated results, in forms that help you interpret them. Graphs are a powerful tool for this subsection. When you include graphs, be sure to label them properly, and talk about them in your discussion. A good sample graph from a student report appears in Figure 5 below. In most reports, this subsection also will include tables of numerical results. When calculations are involved, you should show one example of each type of calculation (please do not provide extensive numerical calculations). A sample table from a student report appears in Figure 6. Perhaps the most important aspect of your report is the task of analyzing the results, such as comparing expected and actual results. This discussion should be quantitative whenever possible. Be sure to include percent errors or other indication of deviations from expectations. Be aware of significant digits in your data and calculations. Keep in mind that engineering is about *interpretation* of results much more than generation of results. The results subsection is the usual place to address study questions given in the lab manual.

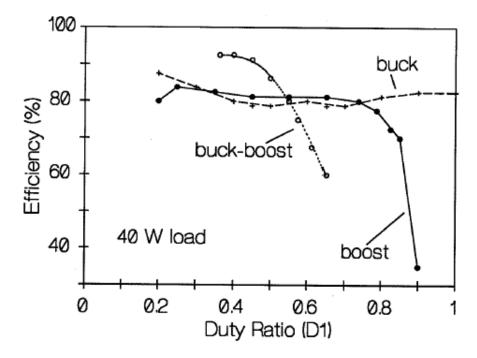

Figure 3: Efficiency vs. Duty Ratio for Dc-Dc Converters

Figure 5. Sample graph from student report.

#### →Error Discussion

In most reports, it is important to point out sensitive places in the data. The issue is to determine the level of confidence in the results. Error issues should be discussed in quantitative terms. Consider the following example, from a student report:

TABLE 1.3 Third Test Setup

L = 370 uH C = 50 uF/ 50 v R = 16 ohm/55 watts Period = 30.5 usec Switching Freq. = 32.79K Hz

| Vin   | Iin .        | Pin          | Vload                              | Iload | Pload        | Vfet         | D2    | Ripple | Po/Pin               |

|-------|--------------|--------------|------------------------------------|-------|--------------|--------------|-------|--------|----------------------|

| Vdc   | Adc          | W            | Vdc                                | Adc   | W            | Vdc          |       | Vpp    | <b>X</b> .           |

| 12.00 | 3.83<br>7.45 | 46.0<br>67.1 | 24.10<br>24.00<br>24.00<br>achieve | 1.577 | 39.9<br>39.1 | 5.8<br>-10.0 | 0.482 | 1.72   | 94.0<br>86.8<br>58.3 |

Figure 6. — Sample table from student report

"The calculated results depend on the phase measurements in Part I. These were hard to make and may not be very exact. Since the frequency was 50,000 Hz, 1° is only 56 ns. The scope gives up to 3% time error. On the 10 µs scale, this is 300 ns. So the measured phases could be 6° off. Our results are a lot better than this, so maybe the scope has less error."

- 4. **Conclusion**. A brief summary of the results and significant problems uncovered by the work. These should represent the actual results as opposed to any expectations you might have had. This is a good place to suggest how you would do it differently if you were to repeat the experiment.

- 5.References. A list of any references used. Please be aware of University regulations involving written work. Quotations or paraphrases from other works, including the lab manual, must be properly referenced. If the lab manual is the only source you used, you can just list "ECE 469 lab manual" as the reference. When other references are involved, list them in the order used. Examples of the format (IEEE style):

- [1] I. Rotit, *The Basics of PWM Inverters*. New York: Energy Printers, 2018, p. 142.

- [2] E. Zeedusset, "Phase error effect in bridge converters," *IEEE Transactions on Industrial Electronics*, vol 61, pp. 4231-4236, October 2014.

- In the text, you should use the reference numbers. For example, "... methods for PWM control are described in depth in [1]...," or "... are discussed in detail in the ECE469 lab manual."

- 6.Appendix. This must include copies of the original data sheets. Number the sheets if you refer to them in the discussion. The appendix should also include any auxiliary information such as semiconductor manufacturer's data sheets, a summary of the procedures actually used, and an equipment list if it differs from that in the lab handout. It is not necessary to include copies of material from the lab manual.

Lab reports should not be lengthy. Except for the Design Project report (which covers extra information), the total length of a report, except for the Appendix, *should not exceed twelve double-spaced pages*. This includes

the title page. Lab report grading will address format as well as each of the six major sections. The discussion is most important. More details about grading will be provided by your instructor. To help you in writing the report, there are several study questions given at the end of each experiment write-up. These questions do not substitute for a complete discussion of results, but provide a starting point. They are not to be taken as homework problems to be answered one by one in the lab report, but rather as important points that should be addressed in the body of the report. The study questions are of two types:

- Specific questions about results. These might request certain plots or calculations. You are expected to provide the expected information completely in your reports.

- Thought questions. These are intended to guide your thinking when evaluating the results. They should be covered in your discussion, but do not answer them one at a time as if they were test problems.

#### **Instrumentation Notes**

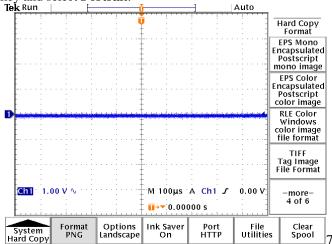

Printing Instructions for the TEK TDS3034 Oscilloscope

The TDS3034 has many I/O modes including TCPIP, GPIB, RS232, and Centronics interfaces. In lab you may choose to save or print traces for your notebook rather than hand-sketch them. Each oscilloscope has an assigned fixed IP number. There are two ways to print traces:

- 1. The complete display can be accessed by entering the scope IP number as a URL in your web browser. The results can be printed or saved as desired. This is usually the simplest method.

- 2. It is also possible to print directly from the instrument. Here are the instructions: Printing to the laser printer:

- 1) Press the *UTILITY* button.

- 2) Press the *SYSTEM* softkey until **Hard Copy** is highlighted.

- 3) Press the *Port* softkey and choose **Ethernet**.

- 4) Press the *Format* softkey and select **LaserJet**.

- 5) Press the *Options* softkey and select **Landscape**.

- 6) Press *Ink Saver* and select **On**.

- 7) Two pages are printed, the first is a banner page with your bench number. The second is your plot.

#### Saving to a disk:

- 1) Press the *UTILITY* button.

- 2) Press the SYSTEM softkey until **Hard Copy** is highlighted.

- 3) Press the *Port* softkey and choose **File**.

- 4) Press the *Format* softkey and select one of the following:

**EPS Mono Encapsulated Postscript mono image** for black and white **EPS Color Encapsulated Postscript color image** for color **TIFF**

5) Press the Options softkey and select **Portrait**.

6) Insert a 3.5" disk label side up into the disk drive.

Power Electronics Laboratory Manual -- Introductory Material

HP 6060B Electronic Programmable DC Load

The HP Programmable load is basically an inverter that accepts dc power and converts it to ac that is then injected into the power grid. It can be extremely useful since it is a versatile, programmable load.

The ratings on the load appear on the front panel and are as follows:

Voltage: 0-60 V

Current: 0-60 A

Max Power: 300 W (notice that this is not the max current at the max voltage)

Always obey these ratings!

How to use the HP Load:

1. Turn the power on.

2. Select what <u>mode</u> you want. The choices are:

Current – it behaves as an ideal current sink

Voltage – it behaves as an ideal voltage source with negative input current

Resistance – you can set a specific resistance

a. Press [MODE]

b. Press either [CURR], [VOLT], or [RES]

c. Press [ENTER]

3. Enter the <u>value</u>:

a. Press the button of the mode you are in, for example: [CURR]

b. Enter on the numeric keypad the value, for example: [5] (for 5 amps)

c. Press [ENTER]

4. [METER] button toggles the display between volt / current and watts

5. **[INPUT ON/OFF]** can be used to disconnect the load

#### Advice:

When you are first trying to get your circuit to work, use a power resistor from the lab stock. This removes the variable of the programmable load. It makes trouble shooting easier since we all know how a plain old power resistor should work. Once the results make sense, you are encouraged to replace the resistor with the active load.

xxi

Demonstration #1 - Introduction

# ECE 469 POWER ELECTRONICS LABORATORY

**DEMONSTRATION #1** — Introduction to the Laboratory

**Objective** — This demonstration is intended to introduce some of the special equipment and methods of the Power Electronics Laboratory. Basic laboratory concepts and safety issues will be reviewed.

**Pre-lab Assignment** — Take a few minutes to read the safety information in the lab manual introductory pages. Be prepared with any questions. Also, be prepared to be quizzed about safety rules.

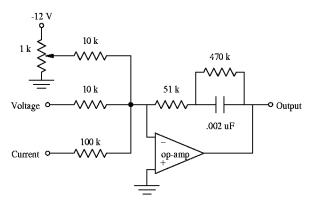

**Introduction** — In this demonstration, the unusual equipment associated with the Power Electronics Laboratory will be described and operated. For each lab station, basic electronic measurement gear is provided. In addition, four custom circuits have been constructed for your use. These are:

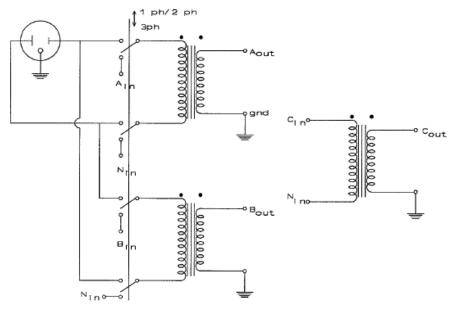

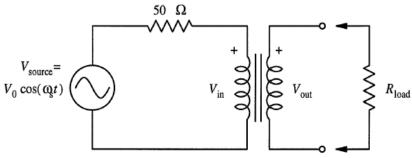

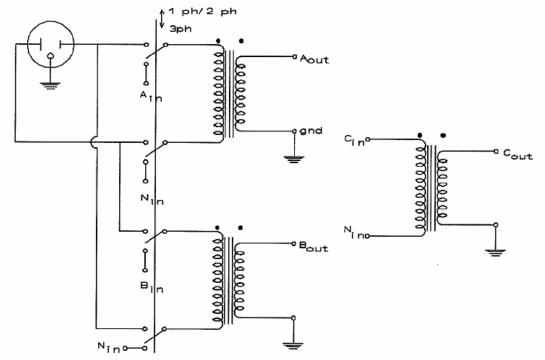

A low-voltage ac supply, from a transformer bank, built into each bench. This supply provides polyphase output, with ratings of 117 V input to 25.2 V output. The switch allows the bank to draw power either from the bench single-phase source or three-phase source. A circuit diagram is shown in Figure 1.

Figure 1. Polyphase transformer bank.

With the panel switch in the "one-phase two-phase" position, A and B outputs are available, with 180° phase shift. The "C" output is indeterminate. With the panel switch in the "three-phase" position, three outputs shifted  $120^{\circ}$  are available (if  $3\phi$  power is supplied to the bench). In both cases, the common neutral point is connected to bench frame ground.

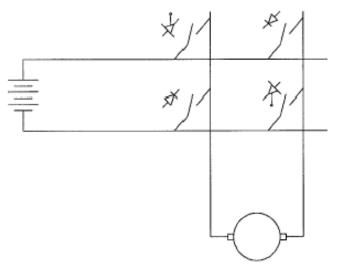

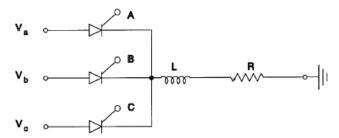

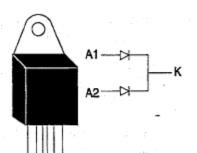

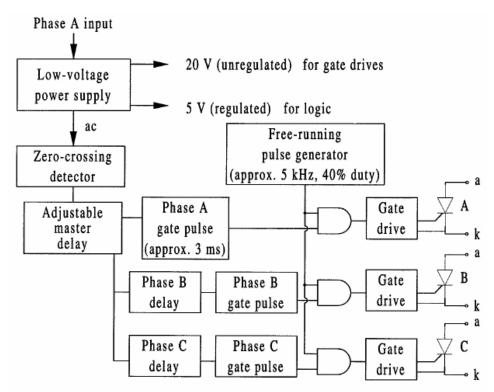

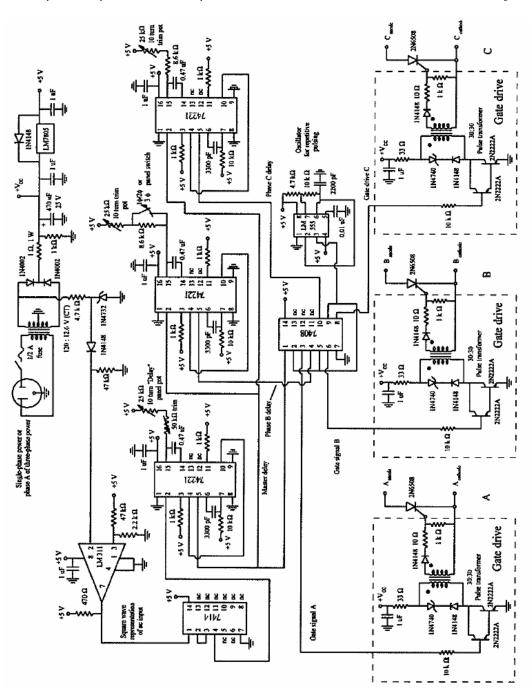

• One-two-three phase SCR control unit. This box contains three silicon controlled rectifiers (SCRs). Each SCR is

controlled by a pulse transformer and is floating with respect to ground. The SCR is similar to a standard diode, except that it does not turn on until a pulse or a switching function is applied to a gate terminal. The three SCRs in the box are operated so that the switching functions are spaced a precise time interval apart, controlled from the front panel.

The "phase" delay value sets the time shift among the three phases. For one-phase or two-phase circuits, it should be set to half the input period — 8 1/3 ms for a 60 Hz input. For three-phase circuits, it should be set to 1/3 of a cycle, or 5 5/9 ms for a 60 Hz input.

The "master" front panel delay control sets the time delay of the SCR "A" signal relative to the input zero crossing. When the value is set at zero, there is no delay. It can be adjusted in milliseconds up to about 40 ms. A front view of the box appears in Figure 2.

Figure 2. Polyphase SCR control unit

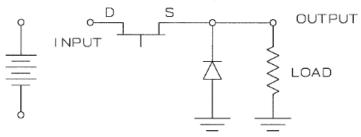

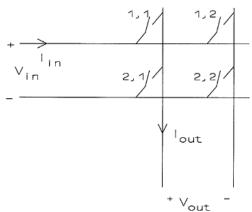

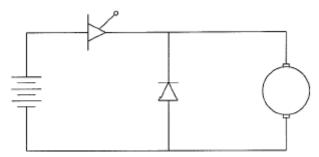

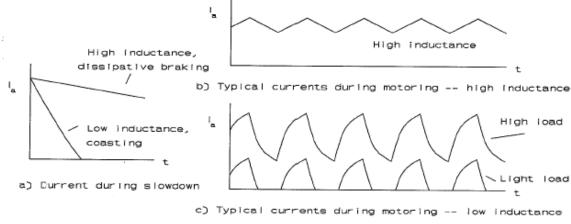

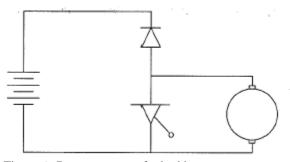

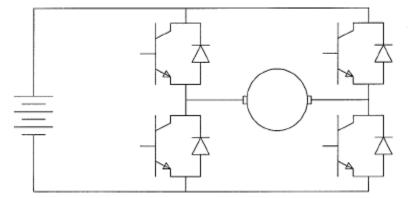

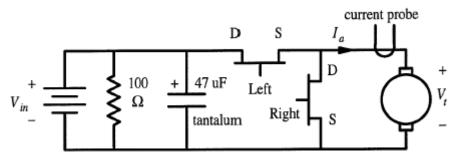

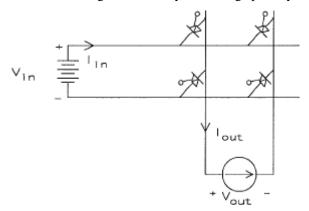

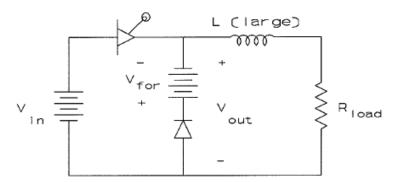

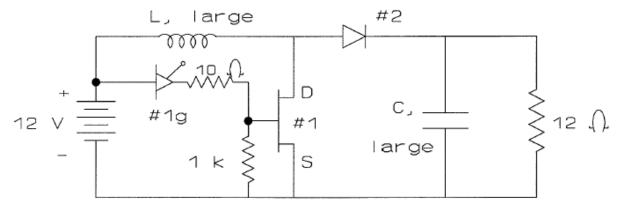

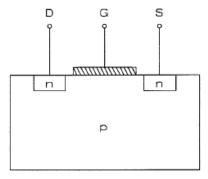

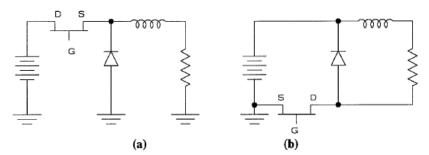

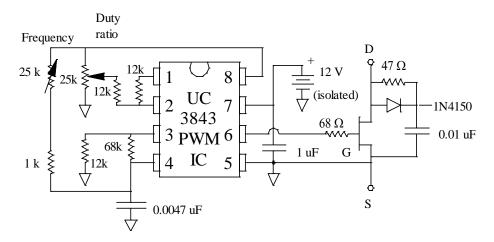

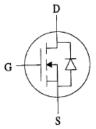

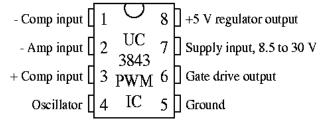

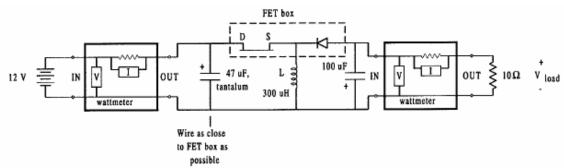

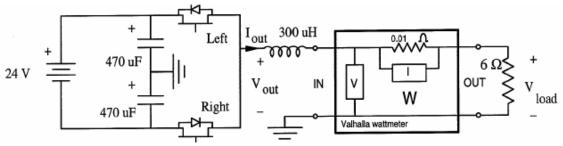

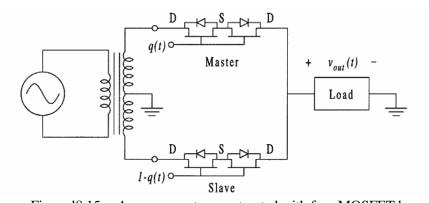

Isolated dual power FET control box. This box contains two field-effect transistors (FETs), each rated for at least 300 V and 15 A. The FET is used as a switch, with either a small resistance (on state) or a very large resistance (off state). The drain and source terminals are floating, and can be connected to any voltage which does not violate the ratings. Also contained in the box is a circuit which operates the FET gates to turn the devices on and off. In essence, a square wave is applied to the FET, turning it on when the square wave is high, and off when it is low. Panel controls adjust the frequency of this square wave, the fraction of the time during which the wave is high, and the action of the square wave on the second FET. The operation is useful for dc-dc and dc-ac conversion applications. For convenience, unconnected power diodes are provided inside the box. A block diagram and a view of the front panel appear in Figure 3.

Figure 3. Isolated FET control unit.

PWM audio amplifier. This small circuit is similar to the FET control box, except that it has been

purpose-built for dc-ac conversion in which the ac waveform is an audio signal. Pulse-width modulation

(PWM) allows a variable signal to control the power delivered to a load.

**Basic Theory** — pPower electronics studies electronic circuits for the conversion of electric power. Examples are units which change dc voltage levels, convert ac to dc or dc to ac, or change the frequency of an ac waveform. Since a converter appears between a power source and a load, and because high power levels might be involved, efficiency is critical. Therefore, such circuits are built up from lossless devices or from low-power control electronics. The possible lossless devices include storage elements (capacitors and inductors), and transformers, but the most important lossless device in power electronics is the switch. A perfect switch has no voltage drop when on and no current flow when off: the power is always zero.

Demonstration #1 - Introduction

Probably the most familiar example of an electronic switch for power conversion is the rectifier diode. A rectifier circuit converts ac waveforms into dc power, with minimal loss. The drawback of simple diode rectifier circuits is the inability to control them. A diode is on whenever current attempts to flow through it in a forward direction, and off otherwise. To improve on this, a family of semiconductor devices known as "thyristors" was invented. The SCR is the most basic thyristor. This device is similar to a diode, except that it need not be on whenever a forward voltage is applied. Instead, turn-on can be delayed until a pulse is applied to a third terminal — the gate. Once the device is on, it functions like a diode. This ability to delay turn-on means that output can be adjusted. Outputs can range from zero (gate always off) to a full waveform equal to that of a diode (gate always on). The SCR is useful in applications which require ac to dc conversion, and power levels beyond 100 MW can be supported with commercial devices. Alternative power devices which can be turned on or off on command also exist. Both field-effect and insulated-gate transistors are used in power electronics for this purpose, along with various more complicated types of thyristors.

**Demonstration Circuits** — For this demonstration, both the SCR and the power FET will be used in converter circuits. The SCR set will be used in a controlled, full-wave rectifier circuit, while the FET unit will be used to form a basic dc-dc converter. These circuits are typical power electronics applications, and many commercial power units are based on them.

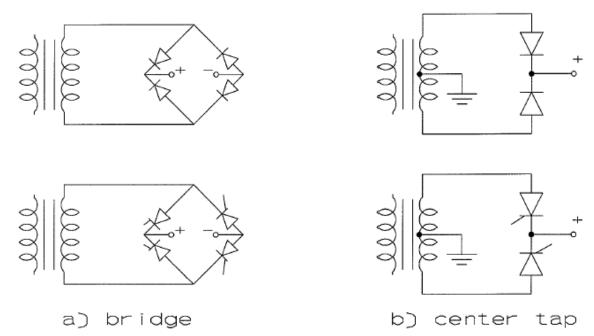

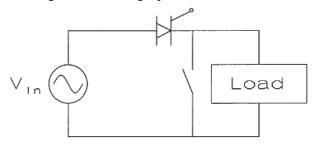

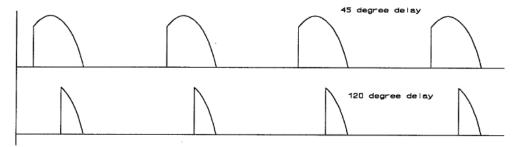

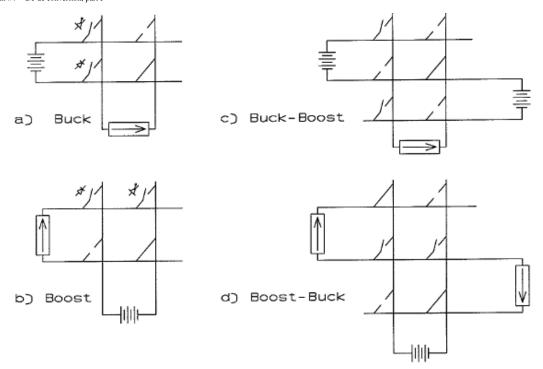

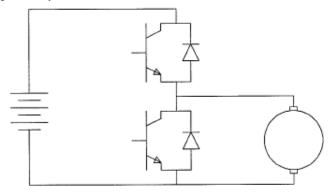

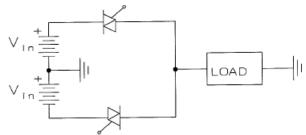

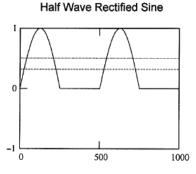

There are two major ways to form a full-wave rectifier, shown in Figure 4. One is with a rectifier bridge, which converts a single ac source into a full-wave rectified waveform. The second uses two diodes with a center-tapped transformer as a "two-phase" ac source. As in the figure, SCRs can substitute for diodes in a full-wave rectifier. The SCRs are operated half a cycle apart, with an adjustable phase angle delay.

The full-wave output is applied to a resistor for this demonstration. When the ac voltage at the top node of the transformer is positive, the top rectifier is forward biased. In the case of the diode, the device will turn on. In the case of the SCR, the device will turn on only if commanded to do so. When the bottom node of the transformer is positive, the bottom diode will be forward biased. Again, the SCR will turn on only when commanded to do so. Part 1 will explore this action.

Figure 4. Basic diode and SCR full-wave rectifier circuits

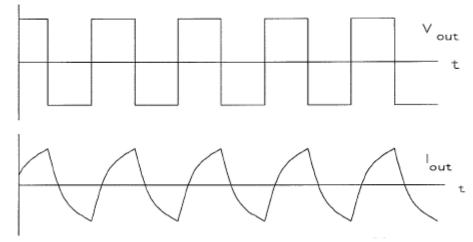

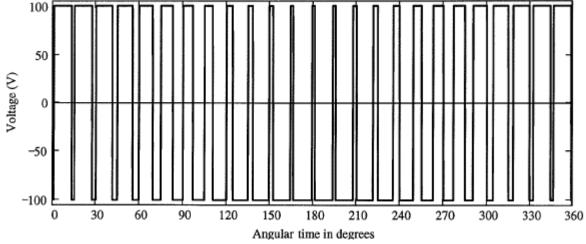

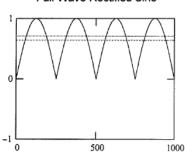

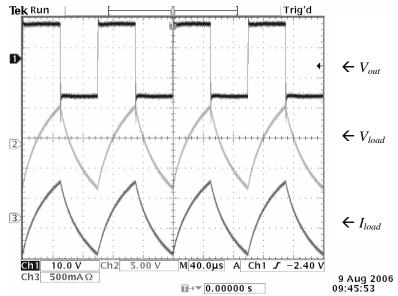

Pulse-width modulation (PWM) is the most popular control tool for dc-dc and dc-ac conversion. When pulse width is adjusted, the average value of a waveform grows larger or smaller, following the width. If a circuit is set up with unipolar dc input, the result is adjustable dc output. If both positive and negative inputs are provided, an ac output is possible when pulse width is adjusted gradually. Parts 2 and 3 examine PWM and its applications.

#### **Procedure**

Part 1 — Rectifiers and the SCR box

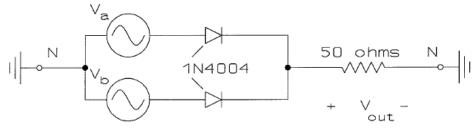

- 1. Connect the 25 V ac supply for two-phase operation. Connect two 1N4004 diodes for full-wave output (anodes to phase A and B output, cathodes in common to load). See the figure below.

- 2. Connect a load of approximately 50  $\Omega$  from the common cathode to ground. What should the resistor power rating be?

- 3. Observe the resistor voltage waveform. Observe diode current and comment. Measure the resistor RMS voltage, RMS current, power, and average voltage. What is the relevance of each?

- 4.Repeat the tests with SCRs in place of the diodes. Connect the 25 V ac supply for two-phase operation as in the figure below. Phases A and B should be wired to anodes A and B of the SCR box.

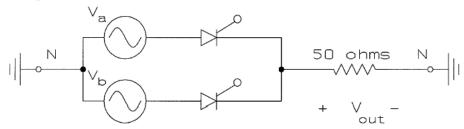

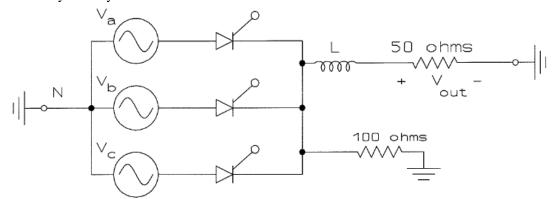

Figure 5. Two-phase diode rectifier test circuit

- 5. Connect the SCR cathodes in common, and to a power resistor of approximately 25  $\Omega$ . The resistor is then connected to supply ground. What power rating must the resistor have?

- 6. With the output enable of the SCR box off, set the phase delay to 8.33 ms for two-phase operation. Set the master delay to 0, then enable the box. Double check all connections, then turn the power on.

- 7.Observe the voltage waveform across the resistor. Notice how the waveform changes as the master delay is altered. Again measure RMS voltage, RMS current, power, and average voltage, and consider the relevance of each.

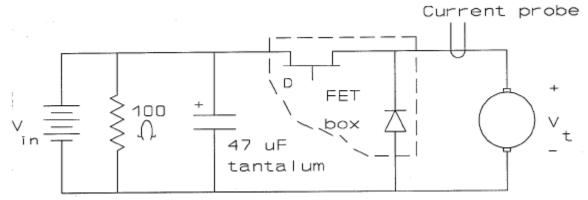

## Part 2 — Dc-dc conversion and the FET box

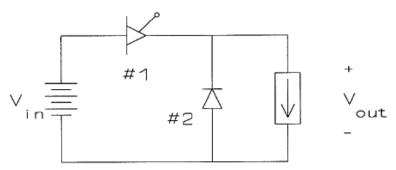

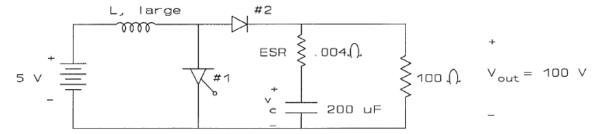

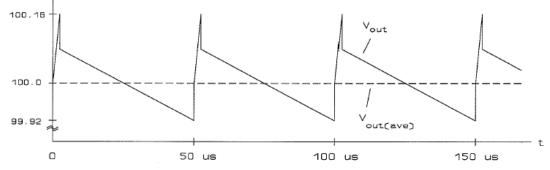

The FET unit will be used in a simple circuit which converts a dc voltage to a lower level with minimal power loss. The output is presented with a rapid switching of the input. The average output level (the dc portion) is lower than the input since the switch is on less than 100% of the time.

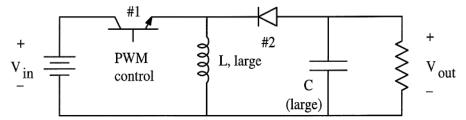

1. Set up the FET control box as shown in the circuit diagram below. Use the left FET in the box.

Figure 6. Simple dc-dc converter circuit

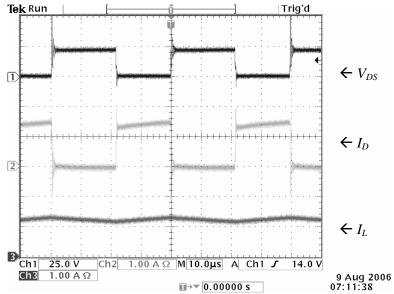

- 2.Observe the drain-to-source voltage. Turn the unit on. Adjust the output for 50 % duty ratio (50 % on time) and about 50 kHz. Disconnect the measuring device.

- 3.Connect a voltage source of 20 to 30 V to the input. Observe the output waveform and average voltage. Adjust the duty ratio and notice the change. Adjust the frequency and notice the change. Explain the results.

## Part 3 — PWM audio amplifier

- 1.Set up the PWM audio amplifier board with a 12 V dc input, CD audio or waveform generator input, and loudspeaker output. The volume should be set to the minimum.

- 2. Connect a voltage probe to the square wave output and a current probe to the loudspeaker. Turn the circuit on.

- 3. Adjust the volume to a low but audible level. Can you see the variation in the pulse widths?

- 4. Observe the change in behavior as the volume increases. Explain the behavior.

**Discussion and Conclusions** — We have performed some basic experiments with power electronic converters. It is hoped that this introductory demonstration will help you work in the laboratory. The following group of study questions will be useful to consider in future reports:

- 1.In dc output converters, what is the relevance of RMS output voltage? What about average voltage? (Hint: consider the effects on loads which are purely resistive, and on loads that include low-pass filtering.)

- 2. Why do we operate the A and B SCRs one-half cycle apart for the full-wave rectifier?

- 3. For the simple dc-dc converter of Demonstration #1, explain how to predict the average value of output voltage from the input voltage, the switching frequency, and the switch duty ratio (the fraction of the time during which the switch is on).

- 4. Consider how an audio signal relates to the dc-dc converter case. What if the switch duty ratio is adjusted "slowly" over time?

**In preparation for next week's experiment, please obtain a laboratory notebook.** This can be any of several types, but *must be bound and must have pre-printed page numbers*.

Experiment #1 -- Basic Rectifier Circuits

# ECE 469 — POWER ELECTRONICS LABORATORY

**EXPERIMENT #1** — Basic Rectifier Circuits

Experiment #1 -- Basic Rectifier Circuits

**Objective** — Measurement techniques of power electronics will be studied in the context of half-wave and full-wave rectifier circuits. Load effects in diode circuits will be explored. The silicon controlled rectifier (SCR) will be introduced, with an R-C delay circuit for gate control.

**Pre-Lab Assignment** — Read the discussion below. Study the procedure, and bring any questions to class. This experiment is not a long one, *provided that you are familiar with the procedure before beginning*. Solve the following, on a separate sheet, for submission as you enter the lab. Please note that your instructor may elect to provide a different problem.

1.A four-diode bridge is used with an ac voltage source with a RMS value of 250 V and a frequency of 50 Hz to produce a full-wave rectifier. The rectifier can be attached to any of several loads. Sketch the resistor voltage and diode current vs. time for the following three cases. In these assignments and in the lab procedures, "sketch" means to draw the waveshape and its important features, without much regard for numerical values. A sketch represents shape information, as opposed to detailed numerical data. You are encouraged to use tools such as Matlab, Mathematica or MathCad to generate graphs and solutions, but be sure to submit the commands used when you turn in the assignment. The cases are:

a. A purely resistive load of about 25  $\Omega$ .

b.A constant current source with a dc value of 5 A in series with a 25  $\Omega$  resistor.

b.A 200 mH inductor in series with 25  $\Omega$ .

c. A 1000  $\mu$ F capacitor in parallel with 25  $\Omega$ .

#### Discussion —

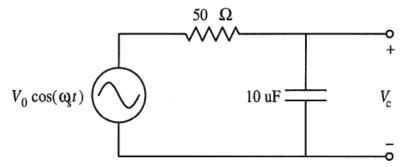

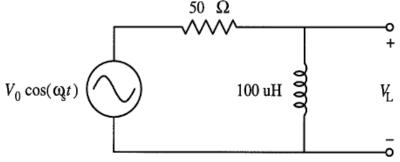

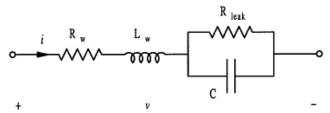

Introduction - A bridge rectifier circuit provides an ac-dc conversion function (rectification). But the waveforms and operation of such a circuit depend on the output load. Furthermore, diodes do not permit any control. This ties the dc output level to the ac input voltage. You have studied the properties of simple R-C, R-L, and R-L-C circuits in previous courses. Properties of "D-C" circuits (diode-capacitor circuits), as well as D-L, D-L-C, and various D-R-x circuits are nonlinear and cannot be studied with familiar linear methods. The behavior of these circuits provides a practical look at power electronic converters, both from the standpoint of energy conversion applications and from the standpoint of laboratory measurements. This is the focus of Experiment #1. Also, the SCR will be introduced, with an R-C circuit applied to provide a time delay in the action of its gate signal.

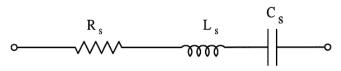

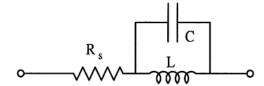

Basic Theory — "Diode" is a general term for an electronic part with two terminals. The most common type of

diode is the rectifier diode (or forward-conducting, reverse-blocking switch). Silicon P-N junction devices and metal-semiconductor junction devices known as "Schottky" diodes are used for this function. Modern silicon diodes have impressive ratings — currents of more than 5000 A can be carried by units which can block reverse voltages of more than 6000 V. Actually, the analysis of diode-based circuits is direct given a single additional consideration. A rectifier diode acts as a switch: It is either on or off. Once this "switch state" is determined, circuit analysis can proceed along conventional lines. The state of a diode — whether it is on or off — is determined uniquely and immediately by the terminal conditions. If forward current flow is attempted, the diode will turn on, and will exhibit only a small residual voltage drop. If reverse current flow is attempted, the diode will turn off and only a minuscule residual current will flow. No third "gate" terminal is needed.

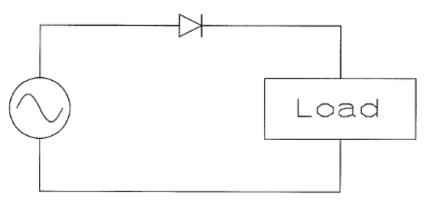

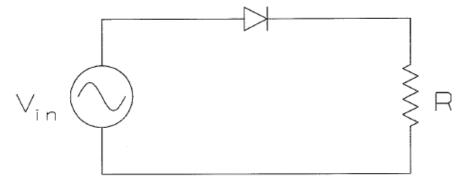

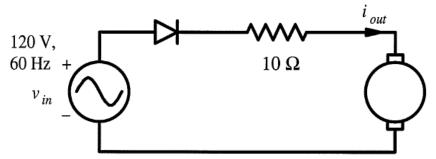

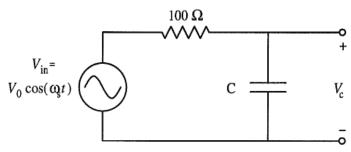

In the half-wave rectifier in Figure 1, the state of the diode depends on the input voltage polarity — and also on the load. With no information about the load, it is *not possible* to predict either the load current or voltage (convince yourself of this; how would one assign the on or off state?). Let us begin with a resistive load, shown in Figure 2. In a resistor, the voltage and current are related by a constant ratio, and the load voltage is zero when the diode is off.

Figure 1. Basic half-wave rectifier diode circuit

One way to find the circuit action (even though we already know what the circuit does), is to take a "trial" approach. For example, consider the case when  $V_{in}$  is positive. We might guess that the diode is off. Then the voltage across the diode is just  $V_{in}$ , which is positive. But an off diode cannot block forward voltage, so the guess was wrong — the diode must be on. Similarly, consider the case when  $V_{in}$  is negative, and guess that the diode is on. Then diode current must be negative. But the diode can only support forward current, and so again the guess is wrong. In reality, the correct guess can be made most of the time. The important principle is that all currents and voltages in a diode circuit must be consistent with the restrictions imposed by the diodes. Even a complicated diode circuit combination can be understood quickly with the trial method. The essence of the method is this:

Once the diode switch state is determined, the circuits are easy to analyze. If we do not know the switch state, we can just assign it in some assumed manner, then proceed with circuit analysis and check for consistency.

Figure 2. Half-wave rectifier circuit with resistive load

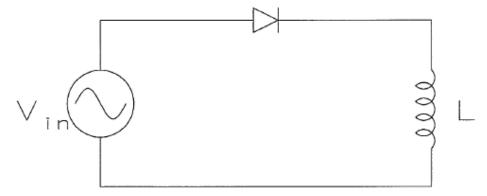

Now, look at the inductive load of Figure 3. Assume that the inductor is large. If current is initially flowing in the inductor, the diode is on. Inductor voltage  $V_L$  will be positive or negative, depending on the input voltage and the inductor current. Since there is current flow, the diode will stay on for some time regardless of the  $V_{in}$  value. If  $v_L = L \frac{di_L}{dt}$  is negative, the inductor current will fall, possibly even to zero. The diode must stay on until the current reaches zero. This time will be delayed relative to the voltage zero-crossing.

Figure 3. Half-wave circuit with inductive load

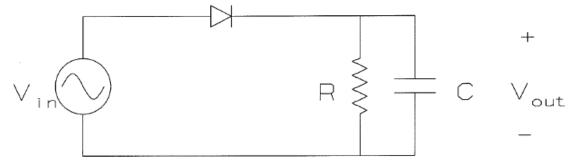

Capacitive loads bring about a different problem. Imagine the capacitor of Figure 4, fully charged and supplying energy to the resistor. As long as  $V_{in} < V_{out}$ , the diode will be off. When  $V_{in}$  becomes larger than  $V_{out}$ , the diode must turn on. But then a large forward current  $i_C = C \frac{dv_c}{dt}$  will flow until  $V_{in}$  becomes less than  $V_{out}$ . Brief, large current spikes are characteristic of diode-capacitor circuits. Such waveforms are typical of the power supplies in cheap electronic equipment. This is not the best situation, since the large current spikes generate noise.

Figure 4. Half-wave circuit with capacitive load

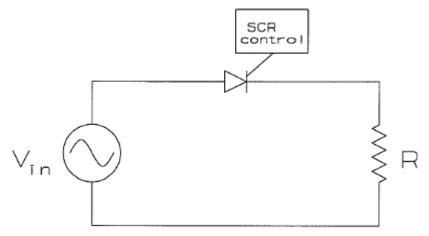

So far, these circuits have no control. The switch necessary to add control still needs to carry current in only one direction, but must be capable of blocking forward voltage when required. The SCR provides this function. The SCR is a triode (three-terminal electronic device), built as a four-layer P-N-P-N configuration. It is called a "latching" device, because the on-state is self-sustaining once it is established. For our purposes, this means that the device is off until commanded to turn on and exactly equivalent to a diode once on. As in Demonstration #1, a set of SCRs can replace the diodes in a simple rectifier to bring about control.

Figure 5. Basic SCR half-wave circuit with resistive load

The basis of rectifier control when SCRs are involved is turn-on delay. Consider the half-wave resistive circuit below. Turn-on of the SCR can be delayed to alter the waveshape. The turn-on delay is traditionally measured in degrees relative to a full diode waveform. The action of this control is not hard to determine for a known load, since the input waveform is being switched on and off.

*Measurement Issues* — In the Power Electronics Laboratory, measurement interpretation is an important ingredient. Many of the waveforms are not sinusoidal, so we will need to supplement conventional measurements with current waveforms, etc.

Experiment #1 -- Basic Rectifier Circuits

The input voltages in a rectifier circuit are sinusoidal ac waveforms, while the intended output is dc. Consider the ac input, which has an average value of zero. A root-mean-square (RMS) measurement would be appropriate for magnitude. Consider the rectifier output. The dc portion (the average value) is of interest. Typical laboratory meters provide the necessary capabilities. For example, the Fluke 45 multimeter displays average value whenever it is set for dc. When set to ac, this meter directs the input through a capacitor, and computes the RMS value of this filter output. Some of the important meter specifications are given in the table below.

| Table I — Summary Specifications of the Fluke 45 Multimeter |                               |                                 |                               |                                |                               |  |

|-------------------------------------------------------------|-------------------------------|---------------------------------|-------------------------------|--------------------------------|-------------------------------|--|

| Quantity                                                    | Dc voltage                    | Ac voltage                      | Dc current                    | Ac current                     | Resistance                    |  |

| Measurement range                                           | 0.1 mV - ±1 kV<br>average     | 0.1 mV - 750 V<br>RMS           | 1 μA - 10 A<br>average        | 1 μA - 10 A<br>RMS             | 0.01 Ω - 300<br>MΩ            |  |

| Valid frequencies                                           | 0 Hz (rejects ac above 20 Hz) | 20 Hz - 100<br>kHz (rejects dc) | 0 Hz (rejects ac above 20 Hz) | 20 Hz - 20 kHz<br>(rejects dc) | _                             |  |

| Error                                                       | ±0.02% of reading, ± 2 digits | ±0.2% of reading ± 10 digits    | ±0.05% of reading, ±2 digits  | ±2% of reading, ±10 digits     | ±0.05% of reading, ± 8 digits |  |

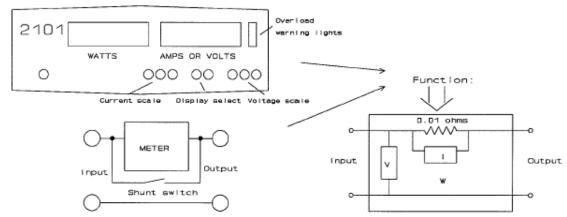

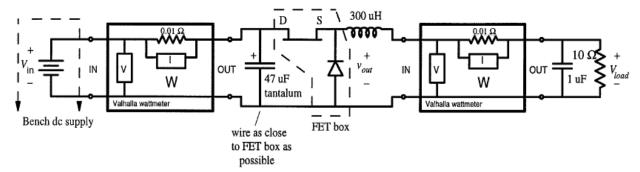

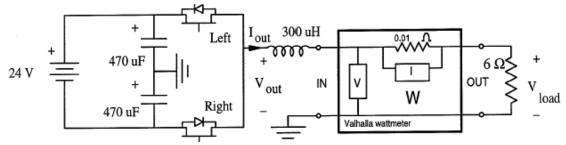

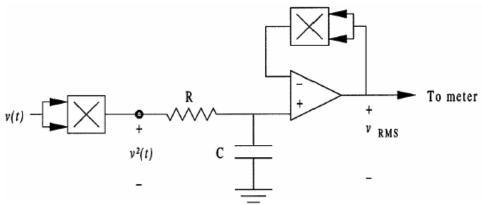

Often, a waveform we measure will contain both dc and ac. The "full RMS" value might be useful in this case. Power is also an important quantity. The Valhalla model 2101 and similar 2111 voltage-current-power meters will be useful for these kinds of measurements. These instruments perform the arithmetic necessary to find actual RMS and  $P_{ave}$  values. They have a standard voltage input, and include a 0.01  $\Omega$  series resistor for sensing current. A front view of the 2101 with its panel connections is shown in Figure 6. The voltage to be sensed is applied in parallel with the input. The output connection forces the current to flow through the sensing resistor. The shunt switch should be *off* in operation. Its purpose is to direct current around the meter if needed to avoid short high-current exposure. An input signal at 0 Hz and 40 Hz-10 kHz will give a true RMS display, as long as the value is within the meter range. Error is shown in Table II. Current from 10 mA to 20 A, and voltage from 1.5 V to 300 V can be measured.

Figure 6. Front panel view of Valhalla model 2101 meter and mount, with function block.

| Table II — Summary Specifications of the Valhalla Scientific 2101 wattmeters |                                                                 |                                                                                                   |                                                                             |  |  |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| Quantity                                                                     | Voltage                                                         | Current                                                                                           | Power                                                                       |  |  |  |

| Measurement range                                                            | 5% to 150% of selected<br>range, up to 300 V rms, 750<br>V peak | 5% to 150% of range, up to<br>20 A rms, 35 A peak.<br>Withstands 100A for 16ms<br>with no damage. | True average power is computed and displayed from voltage and current data. |  |  |  |

| Valid frequencies                                                            | 0 Hz, 40 Hz to 50 kHz                                           | 0 Hz, 40 Hz-50 kHz                                                                                | 0 Hz, 40 Hz- 50 kHz                                                         |  |  |  |

| Error, 0 & 40-<br>5000 Hz                                                    | ±0.1% of reading ±6 digits                                      | ±0.1% of reading ±6 digits                                                                        | ±0.25% of reading ±6 digits                                                 |  |  |  |

| Error, 5-15 kHz                                                              | 0.5% of reading ±6 digits                                       | ±0.5% of reading ±6 digits                                                                        | ±0.5% of reading ±0.5% of range                                             |  |  |  |

| Error, 15-20 kHz                                                             | ±0.75% of reading ±6 digits                                     | ±0.75% of reading ±6 digits                                                                       | ±1% of reading ±1% of range                                                 |  |  |  |

| Error, 20-50 kHz                                                             | add 1% per 10 kHz above 20 kHz                                  |                                                                                                   |                                                                             |  |  |  |

Like current magnitudes, current waveforms can be observed by using a low-impedance series sensing resistor. An alternative that does not introduce grounding problems is to sense the magnetic field produced by flowing charges. The laboratory is equipped with Hall-effect current probes for exactly this function. These probes can measure current from 0 to 12 A (peak) at frequencies between 0 and 50 MHz. One drawback is that the probes have an internal dc offset which drifts for about twenty minutes during warm-up. A second is that they are rather delicate. You will probably find these drawbacks minor compared to the information that can be gained.

Experiment #1 -- Basic Rectifier Circuits

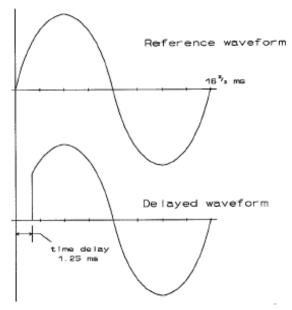

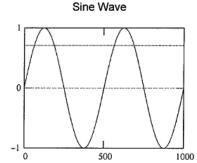

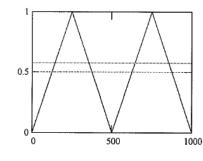

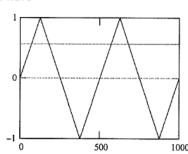

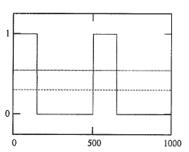

Timing is critical in the operation of most power converters. Since switches are the only means of control, the exact moment when a switch operates is a key piece of information. Consider the waveforms in the figure below. A sinusoidal waveform (perhaps the input voltage to a rectifier) serves as a timing reference. It is straightforward to measure the time shift between this wave's zero crossing and the turn-on rise of the switched signal below it. The example in the figure shows two 60 Hz waveforms. The time delay  $\tau_d$  can be measured directly from the graph as about 1.25 ms. Since a full 360° degree period lasts 16.667 ms, an angle  $\varphi_d$  can be calculated from  $\tau_d$  as

$$\phi_d = \frac{1.25ms}{16.667ms/cycle} \times \frac{360^\circ}{cycle} = 27^\circ$$

One important detail in making this measurement is to make sure both oscilloscope traces are being triggered simultaneously. Make sure the scope is not in an "alternating" waveform mode, and that a single trigger signal is used.

Figure 7. Phase delay measurement example

#### Procedure —

Part One — The Diode

To permit testing with small inductors and capacitors, we will use a waveform generator for the early parts of today's experiments. Please use care in connecting and operating this instrument. It is not designed to supply high current.

- 1. Obtain a toroidal or audio power transformer from the lab selection.

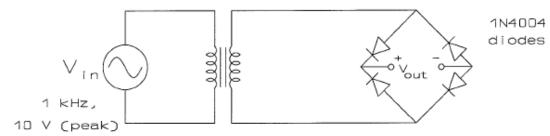

- 2. Construct the circuit shown in Figure 8. Diodes should be standard 1N4001 or 1N4004 rectifiers, or similar.

Figure 8. Rectifier test circuit

- 3.Be careful with ground connections. Set the waveform generator for approximately 1 kHz output at about 10 V peak. Observe  $V_{out}$  with the scope.

- 4. Quickly sketch the output waveform under "no load" conditions (the scope probe gives a slight load).

- 5.Load the bridge with a 500  $\Omega$  resistor (compute the necessary power rating first!). Observe and sketch the output waveform. Use the current probe to observe and sketch the current out of the transformer.

- 6.Connect an inductor, specified by your instructor, in series with the resistor. Observe and sketch the resistor voltage waveform and the current into the bridge. Measure the average resistor voltage with a multimeter.

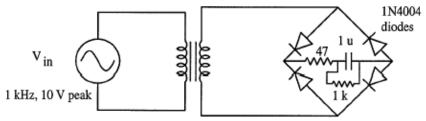

- 7.Remove the R-L load. Instead, attach a 47  $\Omega$  resistor in series with an 1  $\mu$ F capacitor. Place a 1  $k\Omega$  resistor across the capacitor terminals. Observe and sketch the capacitor voltage waveform and the bridge input current waveform. Also measure the average capacitor voltage.

Figure 9. Rectifier test circuit with RC load.

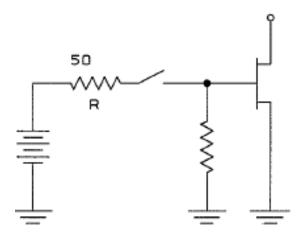

## Part 2 — The SCR

In Demonstration #1, we saw a simple controlled rectifier example, and the waveforms which result. The gate control was described as a pulse, but was not observed or controlled. Today, we will actually operate an SCR with external control, in order to gain some feeling for the gate signals expected.

1. Construct the circuit shown below. The input source should be one terminal from the 25 V 60 Hz supply.

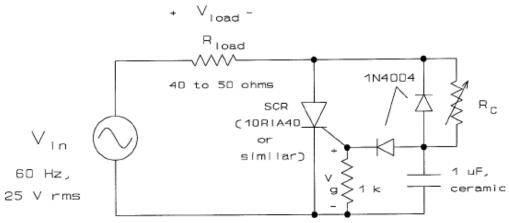

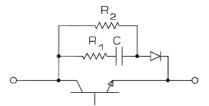

Figure 10. SCR rectifier test circuit

2.Use a 10 k $\Omega$  potentiometer or a resistor substitution box for  $R_c$ . Observe the  $V_g$  and  $V_{load}$  waveforms for  $R_c$  values of 0, 200, 400, 600, 800, 1000, and 1200  $\Omega$ . Sketch the two waveforms for two or three values of  $R_c$ . Measure the turn-on delay by comparing  $V_g$  or the gate current with  $V_{load}$  with the oscilloscope set for line triggering. Also, use the meters to measure the average and RMS values of  $V_{load}$  in all cases.

## **Study Questions:**

- 1. For part 1, what waveforms would you expect for R, R-L, and R-C loads? Hint: think in terms of low-pass or high-pass filtering.

- 2.Compare the actual waveforms with those expected. Compute the actual circuit time constants, and discuss how they might affect the waveforms.

- 3. The R-L and R-C cases of part 1 represent different output filter arrangements for a rectifier circuit. Discuss the circumstances under which each of these will be effective for generation of dc output.

- 4.Comment on how the diode forward voltage drop (about 1V) affects the waveforms.

- 5. From the part 2 data, tabulate and plot the average load voltage vs. the value of  $R_c$ .

- 6. Compute the SCR gate circuit R-C time constants. Is the turn-on delay governed by RC?

- 7. The circuit shown in Fig. 10 is similar to that used in light dimmers. Can you suggest other applications?

- 8. Could a battery be substituted for the load resistor in Figure 10 to form a controlled charger?

# ECE 469 — POWER ELECTRONICS LABORATORY

${\bf EXPERIMENT~\#2-Ac\text{-}Dc~Conversion, Part~I: Single-Phase~Conversion}$

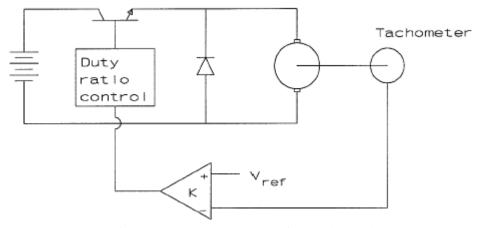

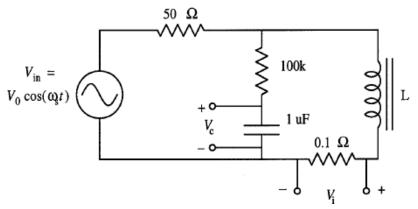

**Objective** — This series of two experiments will examine the properties of controlled rectifiers, or ac-dc converters. The first experiment will concentrate on the single-phase (half-wave) circuit, while the second will examine two- and three-phase converters. Converter concepts such as source conversion and switch types will be studied. Popular applications such as battery chargers and dc motor drives will be introduced.

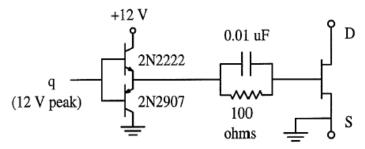

**Pre-Lab Assignment** — Read this experiment. Study the procedure, and bring any questions to class. Solve the following on a separate sheet, for submission as you enter the lab. The dc motor can be modeled as a constant voltage proportional to speed. For this particular motor, the constant is 50 V per 1000 RPM. Please neglect any series inductance. Your instructor may elect to provide a different problem.

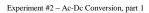

1.A dc motor control circuit is shown below. It is drawing an average current of 1 A. Study it, and answer the following.

Figure 1. Motor supply circuit for pre-lab assignment

- a) Sketch the waveform for the motor current.

- b) Find the motor speed.

- c) Now, given the motor speed, refine your current waveform to make it an accurate plot.

- d)Repeat a), b) and c) using a four-diode bridge instead of a single diode.

#### Discussion —

<u>Introduction</u> — In Experiment #1, you had a chance to become familiar with the basic action of the SCR, and also studied a number of non-resistive rectifier load circuits. The SCR was seen to support control, since it can block forward voltage until commanded to turn on. In today's experiment, the lab SCR boxes will be used to study controlled-rectifier action in more depth.

The 120 V ac waveform available to us in the lab (or the 25 V ac waveform at our transformer output) is a good voltage source. It provides a consistent sinusoidal ac voltage at current levels from 0 up to many Amperes. In a switched converter network, KVL will not allow us to connect this ac voltage source directly to a dc voltage source. Thus, if the objective is to obtain a controllable dc voltage, the ac source must be converted into current or buffered with some other part before it can be otherwise processed. Many types of loads act to provide current conversion. The source conversion concept is one subject of today's work.

<u>Basic Theory</u> — Switching networks allow efficient conversion of electrical energy among various forms, but one disadvantage is that the KVL restriction does not allow direct energy conversion between different voltage sources. Similarly, energy cannot be transferred directly among different current sources by a switch network. To circumvent these drawbacks, it is necessary to provide intermediate conversions. For example, energy from a voltage source can be transferred to a current source, and then on to another voltage source.

A resistive load is a trivial example of current conversion: the incoming voltage produces a proportional resistor current. This is a far cry from a current source, but it is not a voltage source, and it does result in a conversion function. An inductive load is a better conversion example: the inductor voltage  $V_L = L(di/dt)$  resists any change in current. If L is very large, any reasonable voltage will not alter the inductor current, and a current source is realized. A capacitive load has the opposite behavior. The capacitor current  $i_C = C(dv/dt)$  responds whenever an attempt is made to change the capacitor voltage. If C is very large, no amount of current will change the voltage, and a voltage source is realized.

In Experiment #1, you saw three types of rectifier behavior. With a resistive load, the rectified waveform has a dc component, but has substantial ac components as well. With an inductive load, the current is closer to a fixed dc value. With a capacitive load, current is transferred in large spikes during a fraction of each cycle — a behavior which enhances noise and wear and tear on the electrical parts. The inductive circuit came closest to the desired current source conversion. Many electrical loads, especially motors, are inductive. As a result, most circuits behave in such a way that current does not change much over very short periods of time. In power electronics practice, this behavior, along with the desired source conversion function, means that most loads are treated as "short-term" current sources.

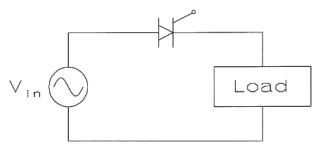

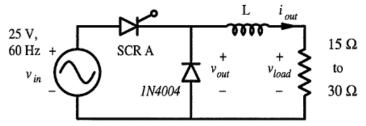

Figure 2. Basic single-phase controlled rectifier

Figure 3. Single-phase converter with second switch for KCL

The basic single-phase controlled rectifier is shown in Figure 2. If the load is inductive, there is no KVL problem. But there is a KCL problem: the switch cannot be turned off if the load is inductive. To see that this is so, observe what happens to L(di/dt) when an attempt is made to turn the switch off. The current must approach zero almost instantaneously. The value of L(di/dt) is a huge negative voltage. In practice, this voltage will likely exceed the blocking capabilities of the switch, which will be damaged. A solution is to provide a second switch across the load, as shown in Figure 3. In simple ac-dc converters, this switch can be a diode, or it can be a second bidirectional-blocking forward-conducting device. Any load which resembles a current source can be taken into account by addition of this second switch.

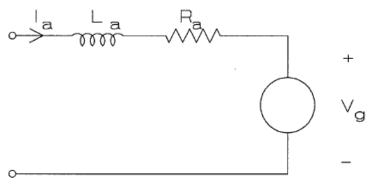

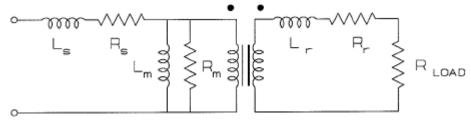

Figure 4. Basic dc motor circuit equivalent

Two popular loads for ac-dc converters are the dc motor and the rechargeable battery. The dc motor has an inductive model, as shown in Figure 4. The motor looks rather like a voltage source, but its windings provide series inductance. This combination has many current-source properties.

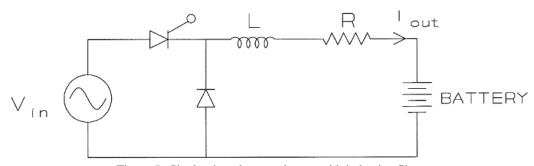

A battery provides a good dc voltage source. To support the desired energy conversion function, something must be placed in series with the battery for current conversion. A resistor can be used, as in the Pre-Lab, with a loss in efficiency. Alternatively, an inductor can be used, as in the circuit of Figure 5. Analysis of this circuit is not trivial. The controlled switch is on whenever  $V_{in}$  is positive. When it is on, the output current is given by

$$\frac{di_L(t)}{dt} = \frac{V_{in} - Ri_L - V_{battery}}{L}$$

When the controlled switch is off, inductor current is

$$\frac{di_L(t)}{dt} = \frac{-Ri_L + V_{battery}}{L}$$

If L is large, the current is approximately constant. These differential equations can be solved to give actual values of current. Charging current is controlled by the resistor value and also by the phase delay used to operate the SCR.

Figure 5. Single-phase battery charger with inductive filter

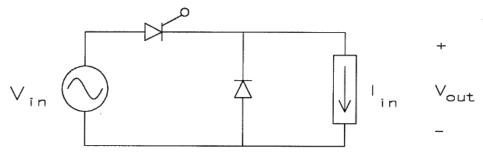

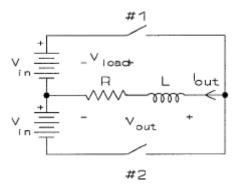

The form of circuit now expected for single-phase conversion appears in Figure 6. The switches are implemented with an SCR and a diode. In this case, the output voltage is  $V_{in}$  whenever the SCR is on, and zero when it is off. The SCR turns off automatically when  $V_{in} \le 0$ . The voltage waveform is a familiar one: a half-wave rectified waveform, possibly with a delayed turn-on. The voltage has an average value given by

$$V_{out(ave)} = \frac{1}{2\pi} \int_{\alpha}^{\pi} \sqrt{2} V_{ac(RMS)} \sin \theta \, d\theta$$

where  $\alpha$  is the angle of delay before the SCR is turned on. This integral can be computed to give

$$V_{out(ave)} = \frac{\sqrt{2}V_{ac(RMS)}}{2\pi}(1 + \cos \alpha)$$

Since the output is a dc current source, average power exists only at dc, and is simply  $I_{out} \cdot V_{out(ave)}$ .

Figure 6. A single-phase ac voltage to dc current converter

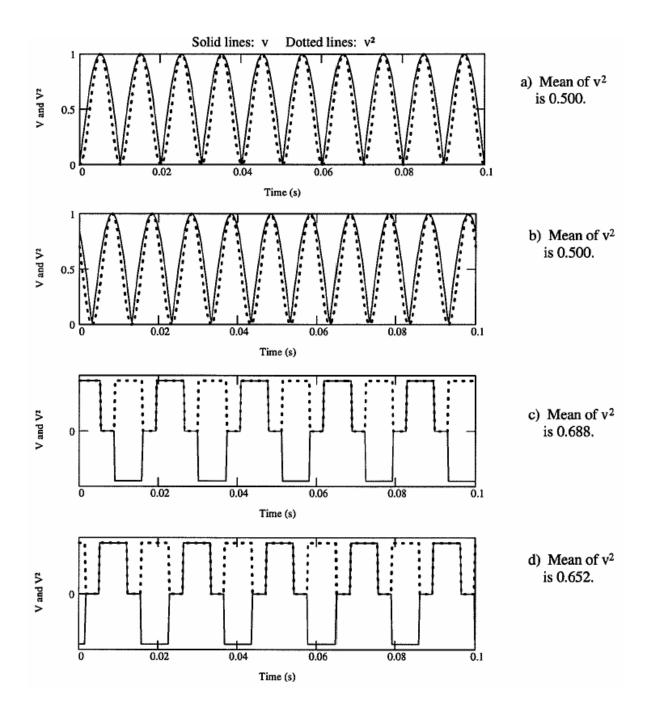

Figure 7. Typical output voltage waveforms

#### Procedure —

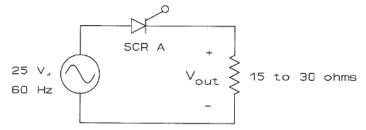

## Part 1: Ideal R-L load

1.Connect phase "A" of the nominal 25 V 60 Hz supply, the SCR labelled "A" in the SCR box, and a resistive load, as shown below. Estimate the required resistor power rating, and abide by it. Remember that the source neutral is grounded. Record the actual RMS value of the source voltage.

Figure 8. SCR test circuit, resistive load